## INTEGRATED CIRCUITS

# DATA SHEET

## PCA9516 5-channel I<sup>2</sup>C hub

Product data

Supersedes data of 2000 Dec 04

File under Integrated Circuits — ICL03

2002 Mar 01

## 5-channel I<sup>2</sup>C hub PCA9516

#### **DESCRIPTION**

The PCA9516 is a BiCMOS integrated circuit intended for application in I<sup>2</sup>C and SMBus systems.

While retaining all the operating modes and features of the I<sup>2</sup>C system, it permits extension of the I<sup>2</sup>C bus by buffering both the data (SDA) and the clock (SCL) lines, thus enabling five buses of 400 pF.

The I<sup>2</sup>C bus capacitance limit of 400 pF restricts the number of devices and bus length. Using the PCA9516 enables the system designer to divide the bus into five segments off of a hub where any segment to segment transition sees only one repeater delay.

It can also be used to run different buses at 5 V and 3.3 V or 400 kHz and 100 kHz buses where the 100 kHz bus is isolated when 400 kHz operation of the other bus is required.

#### **FEATURES**

- 5 channel, bi-directional buffer

- I<sup>2</sup>C-bus and SMBus compatible

- Active high individual repeater enable input

- Open-drain input/outputs

- Lock-up free operation

- Supports arbitration and clock stretching across the repeater

- Accommodates standard mode and fast mode I<sup>2</sup>C devices and multiple masters

- Powered-off high impedance I<sup>2</sup>C pins

- Operating supply voltage range of 3.0 V to 3.6 V

- 5 V tolerant I<sup>2</sup>C and enable pins

- 0 to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115, and 1000 V CDM per JESD22-C101.

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA.

- Package offerings: SO and TSSOP

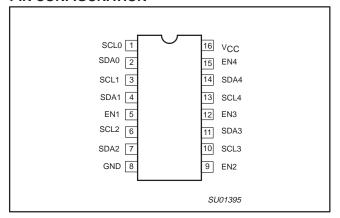

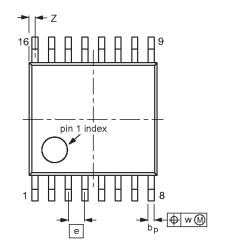

#### **PIN CONFIGURATION**

Figure 1. Pin configuration

#### PIN DESCRIPTION

| PIN | SYMBOL          | FUNCTION                       |  |  |  |  |  |

|-----|-----------------|--------------------------------|--|--|--|--|--|

| 1   | SCL0            | Serial clock bus 0             |  |  |  |  |  |

| 2   | SDA0            | Serial data bus 0              |  |  |  |  |  |

| 3   | SCL1            | Serial clock bus 1             |  |  |  |  |  |

| 4   | SDA1            | Serial data bus 1              |  |  |  |  |  |

| 5   | EN1             | Active High Bus 1 enable Input |  |  |  |  |  |

| 6   | SCL2            | Serial clock bus 2             |  |  |  |  |  |

| 7   | SDA2            | Serial data bus 2              |  |  |  |  |  |

| 8   | GND             | Supply ground                  |  |  |  |  |  |

| 9   | EN2             | Active High Bus 2 enable Input |  |  |  |  |  |

| 10  | SCL3            | Serial clock bus 3             |  |  |  |  |  |

| 11  | SDA3            | Serial data bus 3              |  |  |  |  |  |

| 12  | EN3             | Active High Bus 3 enable Input |  |  |  |  |  |

| 13  | SCL4            | Serial clock bus 4             |  |  |  |  |  |

| 14  | SDA4            | Serial data bus 4              |  |  |  |  |  |

| 15  | EN4             | Active High Bus 4 enable Input |  |  |  |  |  |

| 16  | V <sub>CC</sub> | Supply power                   |  |  |  |  |  |

#### **ORDERING INFORMATION**

| DESCRIPTION                | TEMPERATURE RANGE | ORDER CODE | DRAWING NUMBER |  |  |

|----------------------------|-------------------|------------|----------------|--|--|

| 16-pin plastic SO (narrow) | −40 to +85 °C     | PCA9516D   | SOT109-1       |  |  |

| 16-pin plastic TSSOP       | –40 to +85 °C     | PCA9516PW  | SOT403-1       |  |  |

Standard packing quantities and other packaging data is available at www.philipslogic.com/packaging.

5-channel I<sup>2</sup>C hub PCA9516

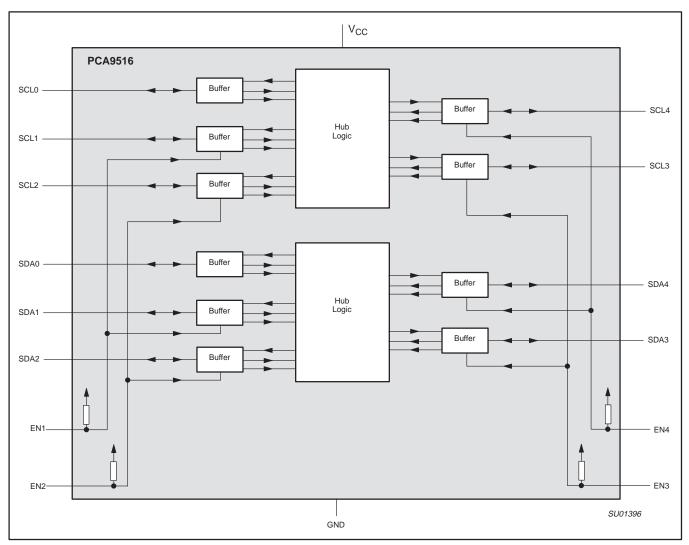

Figure 2. Block Diagram: PCA9516

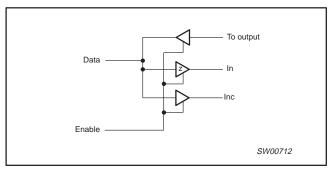

A more detailed view of Figure 2 buffer is shown in Figure 3.

Figure 3.

The output pull-down of each internal buffer is set for approximately 0.5 V, while the input threshold of each internal buffer is set about 0.07 V lower, when the output is internally driven low. This prevents a lock-up condition from occurring.

5-channel I<sup>2</sup>C hub PCA9516

#### **FUNCTIONAL DESCRIPTION**

The PCA9516 BiCMOS integrated circuit is a five way hub repeater, which enables I<sup>2</sup>C and similar bus systems to be expanded with only one repeater delay and no functional degradation of system performance.

The PCA9516 BiCMOS integrated circuit contains five bi-directional, open drain buffers specifically designed to support the standard low-level-contention arbitration of the I<sup>2</sup>C-bus. Except during arbitration or clock stretching, the PCA9516 acts like five pairs of non-inverting, open drain buffers, one for SDA and one for SCL.

#### **Enable**

The enable pins EN1 through EN4 are active high and have internal pull-up resistors. Each enable pin ENn controls its associated SDAn and SCLn ports. When low the ENn pin blocks the inputs from SDAn and SCLn as well as disabling the output drivers on the SDAn and SCLn pins. The enable pins should only change state when both the global bus and the local port are in an idle state to prevent system failures.

The active high enable pins allow the use of open drain drivers which can be wire-ORed to create a distributed enable where either centralized control signal (master) or spoke signal (submaster) can enable the channel when it is idle.

#### I<sup>2</sup>C Systems

As with the standard I<sup>2</sup>C system, pull-up resistors are required to provide the logic HIGH levels on the Buffered bus. (Standard open-collector configuration of the I<sup>2</sup>C-bus). The size of these pull-up resistors depends on the system, but each side of the repeater must have a pull-up resistor. This part designed to work with standard mode and fast mode I<sup>2</sup>C devices in addition to SMBus devices. Standard mode I<sup>2</sup>C devices only specify 3 mA output drive, this limits the termination current to 3 mA in a generic I<sup>2</sup>C system where standard mode devices and multiple masters are possible. Under certain conditions higher termination currents can be used. Please see Application Note AN255 "I<sup>2</sup>C & SMBus Repeaters, Hubs and Expanders" for additional information on sizing resistors and precautions when using more than one PCA9515/PCA9516 in a system or using the PCA9515/16 in conjunction with the P82B96.

#### **APPLICATION INFORMATION**

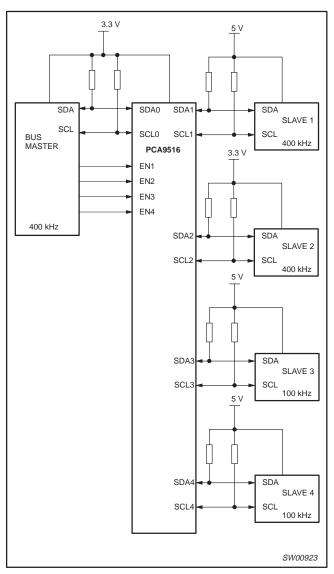

A typical application is shown in Figure 4. In this example, the system master is running on a 3.3 V  $\rm I^2C$ -bus while the slave is connected to a 5 V bus. All buses run at 100 kHz unless slave 3 and 4 are isolated and then the master bus and slave 1 and 2 can run at 400 kHz.

Any segment of the hub can talk to any other segment of the hub. Bus masters and slaves can be located on all five segments with 400 pF load allowed on each segment.

The PCA9516 is 5 V tolerant so it does not require any additional circuitry to translate between the different bus voltages.

When one side of the PCA9516 is pulled low by a device on the  $I^2C$ -bus, a CMOS hysteresis type input detects the falling edge and causes an internal driver on the other side to turn on, thus causing

the other side to also go low. The side driven low by the PCA9516 will typically be at  $V_{OL}$  = 0.5 V.

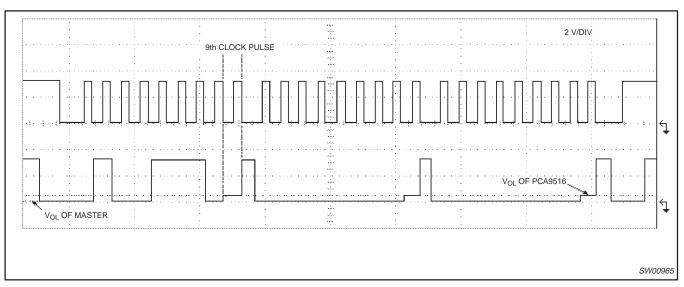

In order to illustrate what would be seen in a typical application, refer to Figures 5 and 6. If the bus master in Figure 4 were to write to the slave through the PCA9516, we would see the waveform shown in Figure 5 on Bus 0. This looks like a normal  $\rm I^2C$  transmission until the falling edge of the 8th clock pulse. At that point, the master releases the data line (SDA) while the slave pulls it low through the PCA9516. Because the  $\rm V_{OL}$  of the PCA9516 is typically around 0.5 V, a step in the SDA will be seen. After the master has transmitted the 9th clock pulse, the slave releases the data line.

Figure 4. Typical application

2002 Mar 01

5-channel I<sup>2</sup>C hub PCA9516

Figure 5. Bus 0 waveform

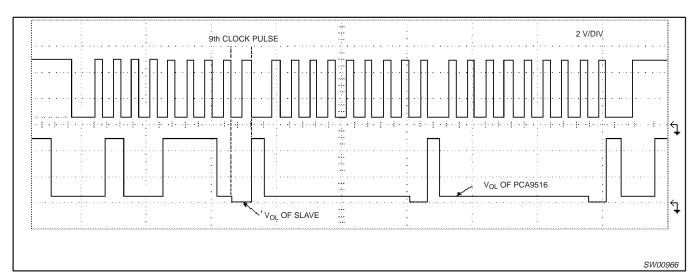

On the Bus 1 side of the PCA9516, the clock and data lines would have a positive offset from ground equal to the  $V_{OL}$  of the PCA9516. After the 8th clock pulse, the data line will be pulled to the  $V_{OL}$  of the slave device that is very close to ground in our example.

It is important to note that any arbitration or clock stretching events on Bus 1 require that the  $V_{OL}$  of the devices on Bus 1 be 70 mV below the  $V_{OL}$  of the PCA9516 (see  $V_{OL}-V_{ilc}\,$  in the DC Characteristics section) to be recognized by the PCA9516 and then transmitted to Bus 0.

Figure 6. Bus 1 waveform

5-channel I<sup>2</sup>C hub

PCA9516

#### **ABSOLUTE MAXIMUM RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134). Voltages with respect to pin GND.

|                        |                                                | LIM         |      |      |

|------------------------|------------------------------------------------|-------------|------|------|

| SYMBOL                 | PARAMETER                                      | MIN.        | MAX. | UNIT |

| V <sub>CC</sub> to GND | Supply voltage range V <sub>CC</sub>           | -0.5        | +7   | V    |

| V <sub>bus</sub>       | Voltage range I <sup>2</sup> C-bus, SCL or SDA | -0.5        | +7   | V    |

| 1                      | DC current (any pin)                           | _           | 50   | mA   |

| P <sub>tot</sub>       | Power dissipation                              |             | 300  | mW   |

| T <sub>stg</sub>       | Storage temperature range                      | <b>-</b> 55 | +125 | °C   |

| T <sub>amb</sub>       | Operating ambient temperature range            | -40         | +85  | °C   |

#### DC ELECTRICAL CHARACTERISTICS

| CVMDOL                            | DADAMETED                                              | TEST CONDITIONS                                                                  |                     | LIMITS |                     |      |  |  |  |

|-----------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|---------------------|--------|---------------------|------|--|--|--|

| SYMBOL                            | PARAMETER                                              | TEST CONDITIONS                                                                  | MIN.                | TYP.   | MAX.                | UNIT |  |  |  |

| V <sub>CC</sub>                   | DC supply voltage                                      |                                                                                  | 3.0                 | 3.3    | 3.6                 | V    |  |  |  |

| V <sub>IH</sub>                   | High-level input voltage                               |                                                                                  | 0.7 V <sub>CC</sub> | _      | 5.5                 | V    |  |  |  |

| V <sub>IL</sub>                   | Low-level input voltage (Note 1)                       |                                                                                  | -0.5                | _      | 0.3 V <sub>CC</sub> | V    |  |  |  |

| V <sub>ILc</sub>                  | Low-level input voltage contention (Note 1)            |                                                                                  | -0.5                | _      | 0.4                 | V    |  |  |  |

| V <sub>IK</sub>                   | Input clamp voltage                                    | I <sub>I</sub> = −18 mA                                                          | _                   | _      | -1.2                | V    |  |  |  |

| I <sub>I</sub>                    | Input leakage current                                  | V <sub>I</sub> = 3.6 V                                                           | _                   | _      | ±1                  | μΑ   |  |  |  |

| I <sub>CCH</sub>                  | Quiescent supply current, both channels HIGH           | V <sub>CC</sub> = 3.6 V;<br>SDAn = SCLn = V <sub>CC</sub>                        | _                   | 7      | 10                  | mA   |  |  |  |

| ICCL                              | Quiescent supply current, both channels LOW            | V <sub>CC</sub> = 3.6 V;<br>one SDA and one SCL = GND,<br>other SDA and SCL open | _                   | 6.8    | 10                  | mA   |  |  |  |

| I <sub>CCLc</sub>                 | Quiescent supply current in contention                 | V <sub>CC</sub> = 3.6 V;<br>SDAn = SCLn = GND                                    | _                   | 7      | 10                  | mA   |  |  |  |

| C <sub>I</sub>                    | Input capacitance                                      | V <sub>I</sub> = 3 V or 0 V                                                      | _                   | 6      | 10                  | pF   |  |  |  |

| I <sub>IL</sub>                   | Input current LOW                                      | V <sub>I</sub> = 0.2 V, SDA, SCL                                                 | _                   | _      | 5                   | μΑ   |  |  |  |

| I <sub>IL</sub>                   | Input current LOW                                      | V <sub>I</sub> = 0.2 V, EN1–EN4                                                  | _                   | 10     | 30                  | μΑ   |  |  |  |

| V <sub>OL</sub>                   | Low level output                                       | I <sub>OL</sub> = 0 or 6 mA                                                      |                     | .52    | 0.6                 | V    |  |  |  |

| V <sub>OL</sub> -V <sub>ILc</sub> | Low level input voltage below output low level voltage | Guaranteed by design                                                             | _                   |        | 70                  | mV   |  |  |  |

| I <sub>OH</sub>                   | Output high level leakage current                      | Output high level leakage current V <sub>O</sub> = 3.6 V                         |                     |        |                     |      |  |  |  |

#### NOTE

V<sub>IL</sub> specification is for enable input and the first low level seen by the SDAx/SCLx lines. V<sub>ILc</sub> is for the second and subsequent low levels seen by the SDAx/SCLx lines.

## 5-channel I<sup>2</sup>C hub

PCA9516

#### **AC ELECTRICAL CHARACTERISTICS**

| SYMBOL            | PARAMETER                   | TEST CONDITIONS    |      | UNIT |      |      |

|-------------------|-----------------------------|--------------------|------|------|------|------|

| STWIDOL           | PARAMETER                   | TEST CONDITIONS    | MIN. | TYP. | MAX. | UNIT |

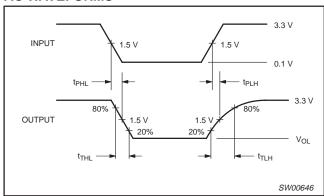

| t <sub>PHL</sub>  | Propagation delay           | Waveform 1         | 57   | 115  | 170  | ns   |

| t <sub>PLH</sub>  | Propagation delay           | Waveform 1         | 33   | 55   | 78   | ns   |

| t <sub>THL</sub>  | Transition time             | Waveform 1         |      | 67   |      | ns   |

| t <sub>TLH</sub>  | Transition time             | Waveform 1; Note 1 |      | 135  |      | ns   |

| t <sub>SET</sub>  | Enable to Start condition   |                    | 100  |      |      | ns   |

| t <sub>HOLD</sub> | Enable after Stop condition |                    | 100  |      |      | ns   |

#### NOTE:

#### **AC WAVEFORMS**

Waveform 1.

#### **TEST CIRCUIT**

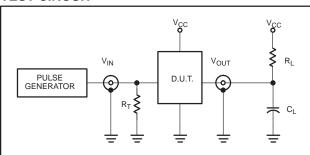

Test Circuit for Open Drain Outputs

#### **DEFINITIONS**

$R_L$  = Load resistor; 1.35 k $\Omega$

C<sub>L</sub> = Load capacitance includes jig and probe capacitance; 7 pF

$R_T$  = Termination resistance should be equal to  $Z_{OUT}$  of pulse generators.

SW00792

2002 Mar 01

The t<sub>TLH</sub> transition time is guaranteed with loads of 1.35 kΩ pull-up resistance and 7 pF load capacitance, plus an additional 50 pF load capacitance. Different load resistance and capacitance will alter the RC time constant, thereby changing the propagation delay and transition times.

## 5-channel I<sup>2</sup>C hub

PCA9516

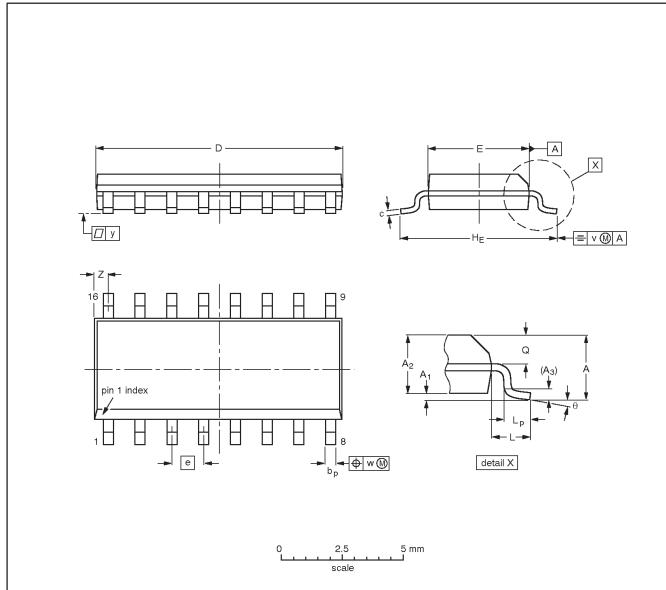

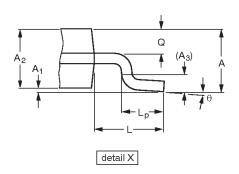

### SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q              | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|----------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 10.0<br>9.8      | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6     | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.39<br>0.38     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 | 0.028<br>0.020 | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |        | REFER  | RENCES | EUROPEAN   | ISSUE DATE                      |

|----------|--------|--------|--------|------------|---------------------------------|

| VERSION  | IEC    | JEDEC  | EIAJ   | PROJECTION | 1330E DATE                      |

| SOT109-1 | 076E07 | MS-012 |        |            | <del>97-05-22</del><br>99-12-27 |

## 5-channel I<sup>2</sup>C hub

PCA9516

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

SOT403-1

#### DIMENSIONS (mm are the original dimensions)

| UNI | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С          | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE         | L   | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|-----|-----------|----------------|----------------|----------------|--------------|------------|------------------|------------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| mm  | 1.10      | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 5.1<br>4.9       | 4.5<br>4.3       | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.40<br>0.06     | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | RENCES | EUROPEAN   | ISSUE DATE                       |

|----------|-----|--------|--------|------------|----------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ   | PROJECTION | ISSUE DATE                       |

| SOT403-1 |     | MO-153 |        |            | <del>-95-04-04</del><br>99-12-27 |

5-channel I<sup>2</sup>C hub PCA9516

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Data sheet status <sup>[1]</sup> | Product status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                   | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                           |

| Preliminary data                 | Qualification                 | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                    | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

<sup>[1]</sup> Please consult the most recently issued data sheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit

http://www.semiconductors.philips.com. Fax: +31 40 27 24825

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

© Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 03-02

Document order number: 9397 750 09513

Let's make things better.

Philips Semiconductors

<sup>[2]</sup> The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.